## 先端技術キーワード解説

## 知っておきたい最新の動き

## [FinFET]

最近、半導体の世界で、FinFET という言葉を頻繁に聞くようになりました。今月(2014年6月)、IC の設計技術に関連する国際学会/展示会である Design Automation Conference (DAC) で、Samsung Electronics が、製造受託のファウンドリーとしてブースを構え、14nm の FinFET プロセスを展示していたとのことです。なお、同時に、台湾のファウンドリーである TSMC も一足先に開始した 16nm の FinFET プロセスを展示していたとのことです。この FinFET とは、どのようなものでしょうか。

FinFET とは、一言で言うと、立体型構造の電界効果トランジスタ(FET: Field effect transistor)です。 絶縁体(酸化物)

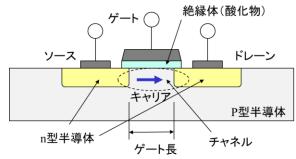

FET とは、現在の大規模 LSI を構成している基本素子です。これまでの一般的なプレーナー(平面)型 FET の代表的な構造を右図に示します。

平面(サブストレート)上にソース(キャリアの発生源)、ドレイン(キャリアの到達部)を配置します。その間をキャリアが流れますが、その部分をチャネルと言います。チャネルの上部に配置したゲートに印可する電圧により、チャネルを流れる電流が制御されます。

・ゲート長が短くなると、オフ時のリーク電流が大 ・チャネルが小さくなると駆動電流が小

FinFET は、プレーナー型 FET に対して、チャネル、ゲートを立体的な構造にしたものです。簡単に言うと、チャンネルが薄い「フィン」状のシリコンで覆われています。つまり、チャネルが立体的なひれ状になっているのです。

この構造は、これまでの微細化、高速化を阻んでいたプレーナー型の限界を打ち破るとされています。具体的には、

- 1) チャネル面積を大きくできることから、駆動電流量を大きくできる。このため、より高速なデバイスを実現できる。

- 2) ゲート長が短くなると現れる短チャネル効果 (オフ時、リーク電流が増える)、パンチスルー現象 (ゲートで制御できない電流が流れてしまう) を抑制できる。このため、微細化が可能となる。などがあります。(右図は、wikipedia「マルチゲート素子」より引用)

ところで、LSI にとって、ブレークスルーのように思える FinFET ですが、最初に提案したのは、久本 大氏という日本の技術者です。日立製作所から、米カリフォルニア大学バークレイ校(UC Berkley)に留学 中の 1998 年、サンフランシスコで開催された IEDM で発表しました。

LSIの世界には、微細化について「ムーアの法則」というものがあります。単なる経験則ですが、不思議なことに、これまで、概ね、この線上に乗って配線ルールの微細化は進展してきました。

しかしながら、今、従来構造の延長では、確実にその限界に近付いているとされています。そして、その限界を越える技術が FinFET とされています。

現在、世界の先端を走っているトップメーカーは、それぞれ、この FinFET に関わっています。前出の Samusung、TSMC に加え、インテル (トライゲート・トランジスタと呼んでいる) なども進めています。 本格的な実用化には、製造技術、コストなどいろいろと課題があるようですが、技術の持つ可能性の果てしなさを感じます。

## (注)

本解説は、執筆当時の状況に基づいて解説をしております。ご覧になる時には、状況が変わっている可能性がありますので、ご注意をお願いします。

Copyright (C) Satoru Haga 2014, All right reserved.